Budapest University of Technology and Economics Faculty of Electrical Engineering and Informatics Department of Measurement and Information Systems

## Practice-Oriented Formal Methods to Support the Software Development of Industrial Control Systems

Ph.D. Dissertation

Dániel Darvas

Thesis supervisor: István Majzik, Ph.D. (BUTE)

Advisor: Enrique Blanco Viñuela, Ph.D. (CERN)

Budapest 2017 Dániel Darvas http://mit.bme.hu/~darvas/

January 2017

Budapesti Műszaki és Gazdaságtudományi Egyetem Villamosmérnöki és Informatikai Kar Méréstechnika és Információs Rendszerek Tanszék

Budapest University of Technology and Economics Faculty of Electrical Engineering and Informatics Department of Measurement and Information Systems

H-1117 Budapest, Magyar tudósok körútja 2.

doi: 10.5281/zenodo.162950

#### Declaration of own work and references

I, Dániel Darvas, hereby declare that this dissertation, and all results claimed therein are my own work, and rely solely on the references given. All segments taken word-by-word, or in the same meaning from others have been clearly marked as citations and included in the references.

#### Nyilatkozat önálló munkáról, hivatkozások átvételéről

Alulírott Darvas Dániel kijelentem, hogy ezt a doktori értekezést magam készítettem és abban csak a megadott forrásokat használtam fel. Minden olyan részt, amelyet szó szerint, vagy azonos tartalomban, de átfogalmazva más forrásból átvettem, egyértelműen, a forrás megadásával megjelöltem.

Budapest, 2017. 01. 11.

Darvas Dániel

"I would therefore like to posit that computing's central challenge, viz. 'How not to make a mess of it', has *not* been met. On the contrary, most of our systems are much more complicated than can be considered healthy, and are too messy and chaotic to be used in comfort and confidence."

Edsger W. Dijkstra [Dij01]

"Funding agencies often require that larger research-funded projects [...] demonstrate the practicality of an approach on 'real' examples. When authors report such efforts, they state that they are successful. Paradoxically, such success stories reveal the failure of industry to adopt formal methods as standard procedures; if using these methods was routine, papers describing successful use would not be published."

David L. Parnas [Par10]

#### Acknowledgements

This dissertation concludes a work that has been started in 2009. I would like to express my gratitude towards everyone who helped me on this long journey:

- My family who supported me through this whole trip;

- My Ph.D. supervisors, István Majzik and Enrique Blanco Viñuela who trusted and supported me, and have guided my work during the last three years;

- My B.Sc. and M.Sc. supervisors, Tamás Bartha and András Vörös who oriented me towards research and helped me much more than any student could ever expect;

- My former and present colleagues and friends at the Fault Tolerant Systems Research Group of the Budapest University of Technology and Economics who provided continuous help, support and fun at work and outside of it;

- My former and present colleagues and friends at the European Organization for Nuclear Research (CERN);

- The PetriDotNet Team for all the improvements and memorable achievements that we have reached together;

- Kinga Györffy, Zoltán Gönye and Tamás Polyák who helped me to understand how to convey a message;

- All the friends who helped to keep me sane while doing research;

- The colleagues at the CERN visits service who let me exercise another passion and to clean my mind;

- The staff of the swimming pools in Ferney-Voltaire and Gex who kept running the facilities where many of the presented ideas were born.

Ágnes, Ákos, András, Attila, Bálint, Borja, Christina, Dávid, Gábor, James, Jesús, Josef, Kristóf, Łukasz, Matěj, Stefan, Tamás, Valentin, Vince, William, Zita, Zoltán, and everyone else I forgot to mention explicitly: thanks for all.

Special thanks to everyone who have read the drafts of my dissertation and provided me feedback, new ideas or corrections.

I would like to thank also the support of CERN, providing the funding of this Ph.D. research project through the Doctoral Student programme.

#### Summary

Formal specification and verification methods provide ways to describe requirements precisely and to check whether the requirements are satisfied by the design or the implementation. In other words, they can prevent development faults and therefore improve the quality of the developed systems. These methods are part of the state-of-the-practice in application domains with high criticality, such as avionics, railway or nuclear industry.

The situation is different in the industrial control systems domain. As the criticality of the systems is much lower, formal methods are rarely used. The two main obstacles to using formal methods in systems with low- or medium-criticality are *performance* and *usability*. Overcoming these obstacles often needs deep knowledge and high effort. Model checking, one of the main formal verification techniques, is computationally difficult, therefore the analysis of non-trivial systems requires special considerations. Furthermore, the mainly academic tools implementing different model checking algorithms are not suitable for users who are not experts in formal methods. The situation is similar with formal specification methods: they are typically too abstract or theoretical to be used by non-specialists, with reasonably long training period.

This work provides various solutions to both the challenges of performance and usability, and centred around the formal verification of industrial control systems. The aim is to provide more efficient verification algorithms and easy-to-use, practice-oriented formal (verification and specification) methods that can be applied to PLC (programmable logic controller) software used in industrial control systems, where the use of heavyweight, low-level methods is not necessary or not feasible. The proposed methods take the particularities of the target domain into account, making formal methods accessible without excessive effort needed.

First, this dissertation provides B-I-Sat, a new algorithm that improves the performance of the saturation-based model checking techniques by combining it with bounded model checking techniques. Saturation-based model checking already provides good performance for many different models. By combining it with bounded techniques, this performance can be further improved in certain cases.

Second, a verification workflow and its implementation are presented that allow the industrial practitioners to use the model checking for PLC-based control software. This is achieved by hiding all formal details and adapting the inputs and outputs of the verification workflow to the specific needs of the domain and the available knowledge. The contributions include a model checker-independent representation of the programs to be verified and property-preserving reduction algorithms to make the formal analysis feasible. Special attention is paid to the verification of safety-critical PLC programs, where development restrictions impose additional needs for the verification workflow.

Third, a formal specification language is proposed that is specifically targeting the behaviour description of program modules used in the PLC-based industrial control software. The language itself is heavily adapted to the domain and its needs. Furthermore, it is complemented by static analysis, code generation and conformance checking methods. For the conformance checking, special relations were introduced, responding to the real needs observed in the domain.

All these contributions are demonstrated and evaluated on real, industrial examples.

#### Összefoglaló

A formális specifikációs és verifikációs módszerek használatával lehetőség nyílik követelmények precíz leírására és annak ellenőrzésére, hogy a követelményeket kielégíti-e egy terv vagy megvalósítás. Más nézőpontból e módszerek segítségével elkerülhetők, illetve felfedhetők és javíthatók bizonyos fejlesztési hibák, ami által a fejlesztett rendszerek minősége javul. A formális módszerek használata mára elterjedt gyakorlattá vált a biztonságkritikus rendszerek, mint például légi, vasúti vagy nukleáris rendszerek fejlesztésében.

Az ipari vezérlőrendszerek területén mást tapasztalhatunk. Mivel e rendszerek jóval kevésbé kritikusak, a fejlesztés során ritka a formális módszerek használata. Ezen módszerek alacsony vagy közepes kritikusságú rendszerek fejlesztésében való alkalmazásának két fő akadálya a korlátozott teljesítmény és használhatóság, amelyek leküzdéséhez gyakran nagy szaktudás és erőfeszítés szükséges. A modellellenőrzés, az egyik gyakran használt formális verifikációs módszer meglehetősen számításigényes, így a nemtriviális rendszerek modellellenőrzése különleges technikákat igényel. Továbbá a modellellenőrző algoritmusokat megvalósító, főként akadémiai eszközök nehezen használhatók a formális verifikációban nem jártas felhasználók számára. Hasonló tapasztalható a formális specifikáció terén is: ezek a módszerek általában túl absztraktak vagy matematikaközeliek ahhoz, hogy nem specialisták komoly képzés nélkül használni tudják.

Jelen munka többféle megoldást nyújt mind a teljesítmény, mind a használhatóság kihívására, fókuszba helyezve az ipari vezérlőrendszereket. A munka célja hatékonyabb verifikációs algoritmusokat és könnyen használható, gyakorlatorientált formális (verifikációs és specifikációs) módszereket javasolni, amelyek felhasználhatók a programozható logikai vezérlők (PLC-k) szoftverének fejlesztésében, ahol a "nehézsúlyú", alacsony szintű módszerek alkalmazása tipikusan nem lehetséges vagy nem szükséges. A javasolt módszerek figyelembe veszik a megcélzott szakterület sajátosságait, így elérhetővé teszik a formális módszerek használatát túlzott erőfeszítés nélkül.

Elsőként egy új verifikációs algoritmus, a B-I-Sat kerül bemutatásra, amely a szaturációalapú modellellenőrzési technikák teljesítményét javítja azáltal, hogy az algoritmust ötvözi a korlátos modellellenőrzési módszerekkel. A szaturációalapú modellellenőrzés már számos modellen bizonyította hatékony működését. Ennek a korlátos módszerekkel történő integrációja tovább javíthatja a teljesítményét bizonyos esetekben.

Másodikként egy verifikációs folyamat és annak megvalósítása kerül bemutatásra, amely lehetővé teszi az ipari fejlesztőknek a PLC-alapú vezérlőprogramok modellellenőrzését. Ez annak köszönhető, hogy a folyamat elrejti az összes, formális verifikáció terén speciális ismereteket igénylő részletet, és olyan be- és kimeneteket definiál, amelyek illeszkednek a szakterülethez és az elvárható ismeretszinthez. A bemutatott kontribúció magában foglalja a verifikálandó programok egy modellellenőrzőfüggetlen leírását és tulajdonságmegőrző redukciós algoritmusokat a hatékonyság növelése érdekében. Különleges figyelmet kap a biztonságkritikus PLC-programok ellenőrzése, ahol a fejlesztési folyamat megkötései befolyásolják a verifikációs folyamatot.

Harmadikként egy formális specifikációs nyelvet javaslok, amely kimondottan a PLC-alapú ipari vezérlőprogramokban használt programmodulok viselkedésének meghatározását célozza. A nyelv figyelembe veszi a szakterületet és annak igényeit. A specifikációs módszer kiegészítésre került statikus analízissel, valamint kódgeneráló és konformanciaellenőrző módszerekkel. A konformanciaellenőrzéshez új relációkat vezettem be, amelyek a szakterület valós, megfigyelt szükségleteihez illeszkednek.

Mindegyik új eredmény valódi, ipari példákon keresztül kerül bemutatásra és értékelésre.

# **Contents**

| 1 | Intr | oduction                                            | Introductio | 1           |

|---|------|-----------------------------------------------------|-------------|-------------|

|   | 1.1  | Preliminaries and Objectives                        | 1.1 Prelim  | 1           |

|   |      | 1.1.1 Introduction to Formal Verification           | 1.1.1       | 2           |

|   |      | 1.1.2 Introduction to Formal Specification          | 1.1.2       | 3           |

|   |      | 1.1.3 Summary of New Challenges                     | 1.1.3       | 4           |

|   | 1.2  | Contributions and Structure of the Dissertation     | 1.2 Contri  | į           |

| 2 | Bou  | nded Model Checking Based on Saturation             |             | 7           |

|   | 2.1  | Preliminaries                                       | 2.1 Prelim  | 8           |

|   | 2.2  | Related Work                                        | 2.2 Relate  | Ģ           |

|   |      | 2.2.1 Bounded Model Checking                        | 2.2.1       | Ģ           |

|   |      | 2.2.2 Saturation-Based Techniques                   | 2.2.2       | ç           |

|   |      | 2.2.3 Bounded Model Checking With Decision Diagrams | 2.2.3       | 13          |

|   | 2.3  | Overview of the B-I-Sat Algorithm                   | 2.3 Overv   | 13          |

|   |      | 2.3.1 Building Blocks                               | 2.3.1       | 13          |

|   |      |                                                     | 2.3.2       | 14          |

|   |      |                                                     | 2.3.3       | 15          |

|   |      |                                                     | 2.3.4       | 17          |

|   | 2.4  |                                                     | 2.4 Compa   | 19          |

|   | 2.5  |                                                     |             | 21          |

|   |      |                                                     |             | 22          |

|   |      | 2.5.2 Evaluation of CTL Operators                   | 2.5.2       | 22          |

|   | 2.6  | <del>-</del>                                        | 2.6 Evalua  | 25          |

|   |      |                                                     |             | 25          |

|   |      | 2.6.2 Execution Time Evaluation on Benchmark Models | 2.6.2       | $2\epsilon$ |

|   |      |                                                     | 2.6.3       | 29          |

|   |      | · · · · · · · · · · · · · · · · · · ·               | 2.6.4       | 32          |

|   | 2.7  | Summary and Future Work                             | 2.7 Summ    | 34          |

| 3 | Mod  | el Checking Critical PLC Programs                   | Model Che   | 37          |

|   | 3.1  |                                                     |             | 38          |

|   |      |                                                     |             | 38          |

|   |      | e e                                                 | 3.1.2       | 39          |

|   | 3.2  | Design of the Verification Workflow            | 40        |

|---|------|------------------------------------------------|-----------|

|   |      | 3.2.1 Challenges                               | 40        |

|   |      |                                                | 40        |

|   | 3.3  | Intermediate Representations                   | 42        |

|   |      |                                                | 43        |

|   |      | <u>-</u>                                       | 47        |

|   | 3.4  |                                                | 47        |

|   | 3.5  |                                                | 48        |

|   | 0.0  |                                                | 49        |

|   |      |                                                | 50        |

|   |      |                                                | 51        |

|   |      |                                                | 51        |

|   | 3.6  |                                                | 52        |

|   | 3.0  | ·                                              | 52        |

|   |      | C                                              | 55        |

|   |      |                                                | 57        |

|   | 3.7  |                                                | 58        |

|   |      | 1                                              |           |

|   | 3.8  |                                                | 60        |

|   |      | Ç                                              | 61        |

|   |      |                                                | 63        |

|   | 3.9  |                                                | 65        |

|   | 3.10 | Summary and Future Work                        | 69        |

| 4 | Form | nal Specification for PLC Modules              | 71        |

| 4 | 4.1  | •                                              | <b>72</b> |

|   | 4.1  |                                                | 73        |

|   |      |                                                | 75        |

|   | 4.2  |                                                | 76        |

|   | 4.2  |                                                |           |

|   |      | 1 0 0                                          | 76        |

|   | 4.0  |                                                | 79        |

|   | 4.3  | ,                                              | 80        |

|   |      | <u> </u>                                       | 80        |

|   |      | <u>.</u>                                       | 81        |

|   |      |                                                | 82        |

|   |      | 1                                              | 85        |

|   | 4.4  |                                                | 87        |

|   |      | 1                                              | 88        |

|   |      | ,                                              | 89        |

|   | 4.5  |                                                | 90        |

|   |      |                                                | 90        |

|   |      | 4.5.2 Semantics Based on Control Flow Automata | 92        |

|   |      | 4.5.3 Generating the Concrete Implementation   | 93        |

|   |      | 4.5.4 Providing Readable Code                  | 95        |

|   |      | 4.5.5 Generation Process                       | 95        |

|   |      |                                                |           |

|   | 4.6  | Conformance Relations and Conformance Checking | 96        |

|   | 4.6  |                                                | 96<br>96  |

|    |        | 4.6.3 Checking the PLC Conformance Relations                 | 103 |

|----|--------|--------------------------------------------------------------|-----|

|    | 4.7    | Evaluation and Usage Examples                                | 107 |

|    |        | 4.7.1 Comparison of PLCspecif and the Collected Requirements | 107 |

|    |        | 4.7.2 UNICOS Re-engineering                                  | 108 |

|    |        | 4.7.3 SM18-PLCSE Safety Controller                           | 110 |

|    | 4.8    | Summary and Future Work                                      | 111 |

| 5  | Sum    | nmary of the Research Results                                | 115 |

|    | 5.1    | Responses to the Challenges                                  | 116 |

|    | 5.2    | Summary of the Proposed Verification Methods                 | 118 |

|    | 5.3    | Summary of the Theses                                        | 119 |

| A  | Prec   | cise Definitions for the B-I-Sat Algorithm                   | 123 |

| В  | Pseı   | adocode of the Bounded Saturation Algorithms                 | 127 |

|    | B.1    | Restarting Bounded Saturation                                | 128 |

|    | B.2    | Continuing Bounded Saturation                                | 128 |

|    | B.3    | Compacting Bounded Saturation                                | 129 |

| c  | Met    | amodel of the Intermediate Representations of PLCverif       | 131 |

|    | C.1    | Intermediate Model                                           | 131 |

|    | C.2    | Other Intermediate Representations                           | 133 |

| D  | Deta   | ails About the STL to SCLr Translation                       | 135 |

|    | D.1    | Semantics of the STL Instructions                            | 135 |

|    | D.2    | Identified Correspondences Between STL and SCL               | 137 |

|    | D.3    | Concepts of the Correctness Proof                            | 137 |

|    |        | D.3.1 Formal Semantics for SCLr                              | 137 |

|    |        | D.3.2 Formal Semantics for STL                               | 140 |

|    |        | D.3.3 Strategy for the Correctness Proof                     | 142 |

| E  | Sem    | antics of PLCspecif                                          | 145 |

|    | E.1    | Timed Automata                                               | 145 |

|    | E.2    | Translation Algorithms                                       | 146 |

|    | E.3    | Mapping from PLCspecif Semantics to IM                       | 152 |

| F  | List   | of Abbreviations                                             | 153 |

| Pu | ıblica | tions                                                        | 155 |

|    |        | Publications Linked to the Theses                            | 155 |

|    |        | Additional Publications (Not Linked to Theses)               | 159 |

|    |        | Additional Work                                              | 159 |

| Bi | bliog  | raphy                                                        | 161 |

# CHAPTER

### Introduction

#### **Preliminaries and Objectives**

Dependability<sup>1</sup> is an integrating concept comprising availability, reliability, safety, integrity and maintainability. This is a desired property, especially for critical systems. A failure is an observable deviation from the system's required behaviour, thus a threat to dependability. The cause of a failure is the propagation of an *error*, which itself is a certain (internal) system state that can result in a failure. The causes of the errors are the faults [Avi+04].

There are various means to attain the attributes of dependability: fault prevention, fault tolerance, fault removal and fault forecasting [Avi+04]. Formal methods are well-known techniques for the prevention of development faults and some of the operational faults, by providing mathematically sound, unambiguous means for the description and verification of the system's requirements [Mar94]. Formal verification and formal specification are getting more and more used in safety-critical application domains where the consequences of a failure are catastrophic [Avi+04; Woo+09]. This can be either because a single failure may cause an accident or loss of life, or it implies a high economic loss (e.g. in avionics [Sou+09], railway systems [LSP07], space applications [Hav+00]), or the undesired consequence affects a large number of systems (e.g. mass-produced processors [Fix08; Kai+09]) causing a high total cost.

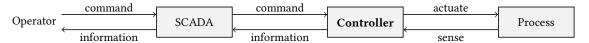

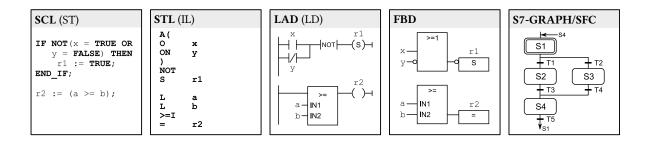

Industrial control systems are used in various settings. If the functionality of a control system is safety-critical, the IEC 61508-2 standard [I61508-2] defines required development and verification methods for each safety integrity level (SIL), depending on the probability of tolerable hazards (hazardous failures). The industrial control systems consist of many components. Often a key element is a programmable logic controller (PLC): a robust, reconfigurable, specialised computer that performs the control tasks. In certain cases, their operation is safety-critical, but many times - due to additional safety-related systems or measures (e.g. physical barriers, independent safety relays) - the target SIL for the PLC-based controller is below SIL 1, the lowest SIL defined in IEC 61508. Even though in these cases the expected failure is rare or not catastrophic, this does not mean that a failure (e.g. an outage) cannot cause significant economic losses. However, the lower SIL typically manifests in reduced verification budget. In these cases the use of heavyweight formal methods (e.g. B Method or Z for specification; or manual use of theorem provers for verification) would need excessive effort. Besides the difficult usage (high training costs, need for special expertise), another common obstacle to using formal verification methods is their performance. For example, exhaustively checking the behaviour

<sup>&</sup>lt;sup>1</sup>In the dissertation the taxonomy proposed by Avižienis, Laprie et al. [Avi+04] is used, which is briefly introduced and summarised in the following two paragraphs.

(state space) of a model is a computationally difficult task, therefore most of the algorithms cannot scale up to the size of industrial problems.

**Goal.** The main goal of this research is to analyse the applicability of formal methods in the domain of industrial control systems and to propose specification and verification methods. As mentioned above, the two main challenges of using these methods are *performance* and *usability*. This dissertation proposes various solutions to both challenges. It aims to provide more efficient verification algorithms and easy-to-use, practice-oriented formal (specification and verification) methods that can be applied to PLC software used in industrial control systems, where the use of heavyweight methods is not necessary or not feasible. The methods to be proposed should take the particularities of the target domain into account.

#### 1.1.1 Introduction to Formal Verification

Verification is "[t]he process of evaluating a system or component to determine whether the products [...] satisfy the conditions imposed at the start" [I1012]. Formal verification techniques are mathematically sound methods to precisely determine the satisfaction of the given formalised requirements.

"Model checking is an automated [formal verification] technique that, given a finite-state model of a system and a formal property, systematically checks whether this property holds for (a given state in) that model" [BK08]. As a more precise definition, model checking is a method to find all states in a model (given as Kripke structure) which satisfy a given temporal logic formula [Cla08]. This method was first described by Edmund M. Clarke and E. Allen Emerson in [CE82], also by Jean-Pierre Queille and Joseph Sifakis independently [QS82].

Being an automated method, it is a good candidate for lightweight formal verification, it has a potential to be a "push-button technology" whose usage does not require high degree of user interaction or expertise [BK08]. Furthermore, it can provide diagnostic traces (counterexamples or witnesses) that is useful feedback about the problems found.

Modelling and requirement description formalisms. While model checking operates on a Kripke structure according to its definition, typically higher-level modelling languages are used for representing the models, such as Petri nets [Mur89], (timed or untimed) automata [AD94], or process algebra [Fok00]. Similarly, multiple different temporal logic can be used to describe the requirements to check. The most frequently used ones are linear temporal logic (LTL) and computation tree logic (CTL). The different formalisms have different expressivity, also the model checking algorithms can differ significantly depending on the supported formalisms.

**Model checking methods.** E. Clarke, one of the creators of model checking said that the model checking algorithm is an "intelligent exhaustive search of the state space to determine if the specification is true or not" [CES09]. With the increase of the number of reachable states in a system, the "intelligence" of the state space exploration algorithms is getting more and more important. The so-called *explicit* methods represent each state of the given model individually. This allows to use simple algorithms from graph theory, but fails to provide solution for large models where the individual handling of each state is not possible. Large state sets (state spaces) may be caused by various reasons, e.g. the large number of inputs and outputs or concurrent behaviours. This is the well-known *state space explosion* problem. Over the years various solutions emerged to handle this issue:

• *Symbolic algorithms*, which store the state space in a more compact, encoded format, e.g. using decision diagrams;

- Abstractions, which simplify the model to have a smaller state space;

- *Bounded algorithms*, which limit the depth of the state space exploration (from the initial state) to reduce the size of the explored state space.

The first symbolic algorithms were based on binary decision diagrams [Bur+92]. Since then new algorithms were developed, using different exploration strategies and data structures. One of the promising solutions is *saturation* [CLS01], which "tends to perform extremely well when applied to discrete-event systems having multiple asynchronous events that depend and affect only relatively small subsystems" [CZJ12]. The fact that the algorithm "performs well" means that the set of verifiable models and requirements is larger or the execution time is shorter, but it does not mean that there are no limitations imposed by the performance needs of the algorithm. In certain cases excessive amount of memory is required to perform the verification.

There is no silver bullet for model checking, each method has its disadvantages and limitations. Some approaches tried already to combine ideas from different methods, e.g. [Cha+02; Cop+01; CNQ05]. A possible improvement of the saturation-based model checking is to combine it with bounded model checking, which – to the author's best knowledge – was not studied before this research project. This could also help the verification of industrial control systems by improving the earlier verification performance (e.g. compared to [c28]). Evaluation of this possibility is a challenge of this dissertation (Challenge 1).

Model checking as a part of the PLC software development process. Model checking has already proven to be useful in various domains [Cla08]. However, providing the necessary formal models and the requirements as temporal logic formulae is a difficult task, especially for the people not familiar with formal methods. Furthermore, model checking may also need manual adaptation, fine-tuning to the current problem to improve the performance. This implies a high cost of usage, which may be an obstacle to apply model checking in the development of PLC programs.

The academic algorithm design and development efforts led to high-performance general-purpose model checkers (e.g. UPPAAL [Amn+01], LTSmin [Kan+15], NuSMV/nuXmv [Cav+14]). However, general-purpose tools cannot improve the domain-specific usability of the verification method. To improve the usability and to integrate formal verification into the industrial control system development processes, the focus should be specifically set to this domain.

Although the use of model checking for PLC-based industrial control software was already studied in e.g. [GSF08; SD08; BBK12], these works did not provide generic solutions applicable in real-life, or this aspect was not emphasised. Making model checking adapted to the PLC program development domain, usable directly by the PLC developers; and making it scalable are challenges of this dissertation (Challenges 2, 3). Furthermore, special attention should be paid to a special branch of PLCs, the so-called *fail-safe* or *safety PLCs*. To attain a high level of confidence during the software development process for such PLCs, special restrictions and development methods are followed (e.g. coding conventions, programming language restrictions), these have to be taken into account for the solution to be proposed (Challenge 4).

#### 1.1.2 Introduction to Formal Specification

Requirements engineering is a set of activities to explore, evaluate and document the objectives, capabilities, constraints and assumptions of a system to be designed [Lam09]. The (requirements) specification is the act of "detailing, structuring and documenting the agreed characteristics of the system-to-be" [Lam09]. According to [Lam00], formal specification "is the expression, in some formal language and at some level of abstraction, of a collection of properties some system should satisfy." One of the

facts making the formal specification process difficult is that "[s]pecifications are never formal in the first place" and they are "hard to develop and assess" [Lam00]. The expected benefits of formalising the specification method are "a higher degree of precision in the formulation [...], precise rules for their interpretation and much more sophisticated forms of validation and verification" [Lam09].

Formal specification is studied since the late 1960s, and since then several methods emerged. Petri nets [Mur89], Lotos [I8807], the B Method [Abr96], Z [I13568], or the communicating sequential processes (CSP) [Hoa85] are widely-known techniques. Though widely-known, they are not widely used in the industry [Kni+97], because they are too complex, they need too deep mathematical knowledge, or their abstraction level is too high. Therefore the usage of these specification methods is restricted to highly critical domains, e.g. avionics [HLR98] or railway industry [But02].

In the industrial control systems domain, the state-of-the-art development processes still rely on informal specifications and hidden assumptions. These specifications are often ambiguous, leading to misunderstanding and unintended behaviours in the implementation. The lack of unambiguous specification imposes a problem for the formal verification too: how can we decide if the implementation is correct, if we do not know what is correctness, i.e. what are the expected properties?

There are various attempts to provide better, PLC-specific specification methods, e.g. [Lju+10; Luk+13]. Analysing the existing methods and finding a suitable specification is a challenge of this work (Challenge 5). It is another challenge to provide formal verification for PLC software on the basis of the selected specification method (Challenge 6).

#### 1.1.3 Summary of New Challenges

- Challenge 1: Designing model checking algorithms combining bounded and saturation-based techniques to improve their performance. Both bounded model checking and saturation-based techniques increase the set of models on which verification is feasible compared to basic explicit model checking algorithms. Is it possible to combine these two approaches? Does it improve the performance with respect to the original saturation-based model checking?

- Challenge 2: Making model checking easily accessible to the PLC developers. Model checking is rarely used for industrial control software, mainly because of the enormous effort needed to create formal models and requirements, furthermore to learn the usage of the model checker tools. How can model checking be made accessible and practically applicable in the PLC program development process? How can model checking be used without excessive effort, without exposing the users (PLC developers) to complex mathematical formalisms?

- Challenge 3: Making the PLC model checking applicable to real-world PLC programs.

The formal models of real PLC modules or programs and their state spaces tend to be extremely large, making the model checking infeasible using general-purpose model checker tools. Could heuristic model reductions reduce the performance needs of model checking and therefore cope with a bigger set of models?

- Challenge 4: Extending the model checking approach to safety-critical PLC programs. The original PLC model checking workflow supported the Siemens SCL language only, which being a high-level language is more suitable for the implementation of complex programs. However, the development of PLCs used in safety-critical settings has specific procedures and restrictions, such as the mandatory usage of FBD or LAD languages (in case of Siemens PLCs). How can model checking be adapted to these lower-level programming

languages used in safety-critical PLC program development?

# Challenge 5: Providing lightweight formal specification for PLC software modules. Unambiguous requirements are essential for any development or verification activity. Formal specifications may reduce the ambiguity, but the general-purpose formal specification methods are too complex and non-intuitive to be used in the PLC development domain with a reasonable effort. What are the requirements towards a formal specification language specially adapted to the PLC domain? What formal specification method can aid the PLC program development process?

**Challenge 6: Providing verification solutions based on formal specification.** How could formal specification improve the PLC program verification? What verification methods can be used to check the conformance between a PLC program and its formal specification? How can this be made useful in practice, without excessive amount of false positives (i.e. without having a high number of detected differences that are considered to be acceptable by the developers)?

These challenges led to a research project with new scientific results in three different areas: a new, saturation-based bounded model checking algorithm with different iteration strategies (Thesis 1), a new method to apply model checking for PLC programs (Thesis 2) and the definition of a formal specification language for PLC software modules together with its application methods (Thesis 3). Table 1.1 presents the correspondence between the discussed challenges and the results of this work.

Table 1.1: Correspondence between the discussed challenges and the proposed solutions

|          |                               |   | С | hal | leng | ge |   |

|----------|-------------------------------|---|---|-----|------|----|---|

|          |                               | 1 | 2 | 3   | 4    | 5  | 6 |

| Thesis 1 | Chapter 2 of the dissertation | • |   |     |      |    |   |

| Thesis 2 | Chapter 3 of the dissertation |   | • | •   | •    |    |   |

| Thesis 3 | Chapter 4 of the dissertation |   |   |     |      | •  | • |

#### 1.2 Contributions and Structure of the Dissertation

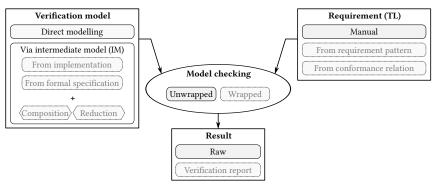

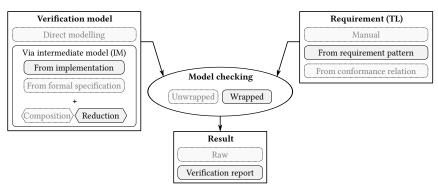

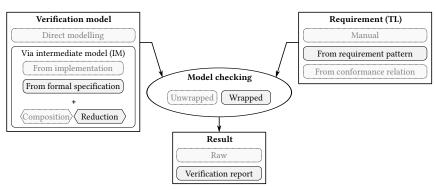

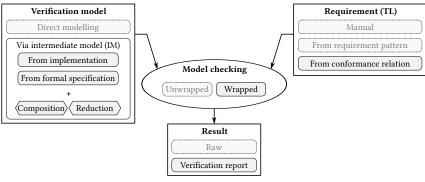

This dissertation presents three different contributions. These contributions are centred around formal verification of industrial control software. The challenges are twofold: they target the performance and the usability of model checking that are two major obstacles of using model checking in real life scenarios. The high-level challenges and the contributions are summarised in Figure 1.1.

• Thesis 1 (Chapter 2) discusses the improvement of saturation, a model checking algorithm which provided good performance for many different models. In this thesis the combination of saturation with bounded model checking will be presented. This new approach may further improve the performance of the saturation algorithms, increasing the set of requirements and models that are possible to be verified. This general method may give a solution for industrial control software when it is not efficient to develop a dedicated workflow for the given use case.

#### Key challenges in formal verification Performance Usability/accessibility 叴 ₹ 亽 叴 Algorithmic improvements Practice-oriented Solutions based on verification workflow formal specification (B-I-Sat) (PLCverif) (PLCspecif) Thesis 2 (Chapter 3) Thesis 3 (Chapter 4) Thesis 1 (Chapter 2) Conformance Code generation checking

Figure 1.1: Overview of the contributions of the dissertation

Here the focus is on the performance improvements, thus it may be an appropriate solution when the performance is the bottleneck of the verification, or when it is not efficient to design and implement a dedicated verification workflow for the given verification case(s).

This thesis responds to Challenge 1 discussed in Section 1.1.3.

• Thesis 2 (Chapter 3) focuses on the usability aspects of model checking applied to PLC-based industrial control software. It provides a verification workflow that makes model checking of PLC programs directly usable by the developers, without requiring extensive training, direct modelling or manual reductions. The presented contributions are related mainly to (i) the intermediate model language used for the model checker-independent representation of the PLC programs, (ii) the reduction heuristics that reduce efficiently the size of the intermediate model representations, (iii) the extension of the verification workflow to support the development and verification of safety-critical PLC programs, and finally (iv) the implementation and the evaluation of the verification workflow.

This part focuses on making model checking of PLC programs accessible to developers. The verification workflow is flexible and it only needs the PLC source code and informal requirements, which are formalised using given requirement patterns by the user.

This thesis responds to Challenges 2, 3 and 4 discussed in Section 1.1.3.

• Thesis 3 (Chapter 4) is dedicated to PLCspecif, a novel complete, formal behaviour specification language specifically targeting PLC modules. Besides the syntax and semantics definition, it is extended with code generation, invariant checking, static analysis and conformance checking facilities, to provide wide support for the development and analysis of PLC software.

This contribution, similarly to Thesis 2, also focuses on the usability improvements of the PLC program verification, but here a more thorough analysis is targeted. This additionally requires the formal specification of the module to be verified, but the benefit is a deeper analysis and the possibility of automated implementation generation.

This thesis responds to Challenges 5 and 6 discussed in Section 1.1.3.

# **Bounded Model Checking Based on Saturation**

Model checking is a successful verification technique, however its usage is limited partially because of its performance. Various solutions emerged during the last 30 years to improve the performance. The so-called saturation algorithms successfully pushed the limits of model checking and increased the set of verifiable problems. Saturation improves the performance by using an efficient state encoding and a special search order. Other approaches, such as bounded model checking use different methods for improvement. During bounded model checking, the model is checked only up to a certain depth, limiting the size and complexity of the model checking problem.

The bounded and the saturation-based model checking use orthogonal ideas for improvements, therefore they could be combined. This may improve the saturation-based model checking techniques by reducing the run time in case of shallow requirements, where the bounded model checking typically excels. Although the high-level ideas of these two approaches are independent, in reality they affect each other. For example, the special search order makes limiting the exploration depth more difficult.

**Goal.** The goal of the work discussed in this chapter is to combine the principles of bounded model checking with the saturation-based techniques, to show its feasibility and to improve the performance of saturation; then to build an iterative bounded saturation-based CTL model checking algorithm and to assess its performance.

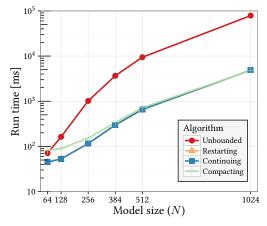

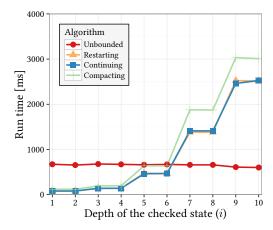

This chapter presents *B-I-Sat* (Bounded Iterative Saturation), an iterative, bounded CTL model checking algorithm using saturation-based techniques. Three different strategies are proposed, which are implementing the B-I-Sat algorithm with minor differences. The termination conditions, a crucial part of this algorithm, are analysed in more detail. The evaluation part shows that these methods improve the performance and scalability of saturation in certain cases, and may improve the applicability of model checking in industrial use cases too.

**Structure of this chapter.** Section 2.1 overviews the background of the work described in this chapter. The corresponding formal definitions can be found in Appendix A. Next, Section 2.2 is dedicated to the related work, with a special focus on the various saturation-based techniques. Section 2.3 discusses B-I-Sat, the novel iterative bounded model checking solution and its challenges. Two strategies, the restarting and continuing strategies are described here as well. The more advanced, so-called

compacting strategy is proposed in Section 2.4. After, Section 2.5 discusses the application of three-valued logic to give termination conditions for the iterative B-I-Sat algorithm. The evaluation of the proposed methods can be found in Section 2.6. Finally, Section 2.7 concludes the chapter.

#### 2.1 Preliminaries

In this section we focus on the key preliminaries that are necessary to understand the contributions presented later. For a more detailed overview we refer to [j2; a30].

**Model checking.** Model checking (see Def. A.1, p. 123) [Cla08] determines whether a given model satisfies the given temporal logic formula (requirement). In general, model checking looks for the state set of a model M that satisfies the given formula f, but often we are interested only whether the initial state  $s_0$  of the model satisfies f, formally: M,  $s_0

otin f$  (or simply denoted as  $s_0

otin f$ ).

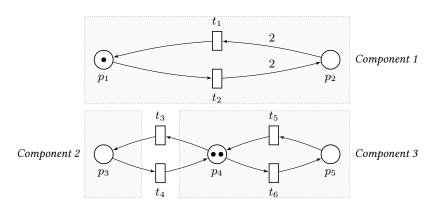

Although the formal definition of model checking typically states that the model is given as a *Kripke structure (see Def. A.2, p. 123)*, modelling real systems using the low-level Kripke structures is often impractical due to the high number of states. Various higher-level models exist with different properties. The Petri net formalism (*see Def. A.4, p. 124*) is one of the widely used modelling methods, which will be used in this chapter as well. An example Petri net is shown in Figure 2.1.

Figure 2.1: Example Petri net

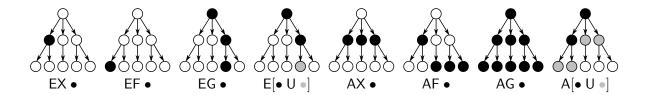

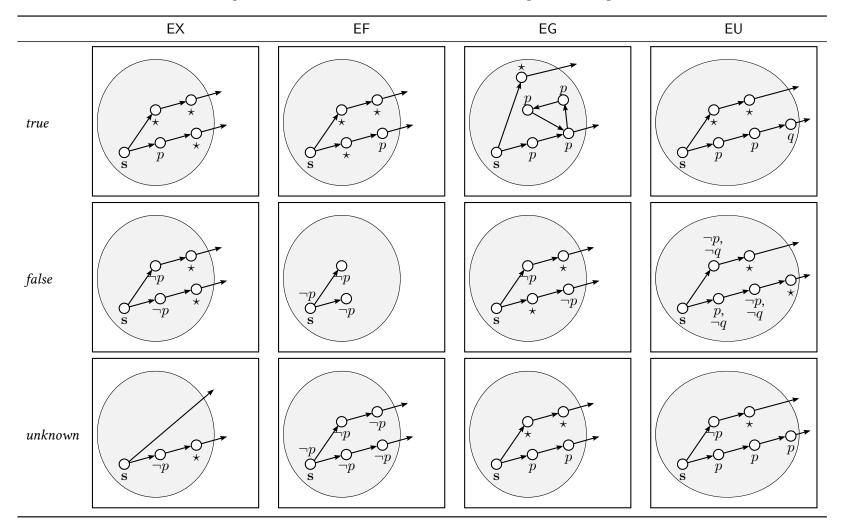

Multiple formalisms exist to define the temporal logic formula too. Two well-known and widely-used formalisms are *computation tree logic* (CTL) and *linear temporal logic* (LTL). As saturation is mainly suitable for CTL [CMS03], we are focusing on this formalism. CTL expressions are interpreted on the *computation tree* (see Def. A.5, p. 124), which is practically a radix tree of all possible paths from the initial state(s). CTL formulae (see Def. A.6, p. 124) [CE82] consist of Boolean expressions that may or may not be true for the individual states, and temporal operators (e.g. EF, EG, AX) which argue about where in the computation tree should a certain Boolean expression be true to satisfy the CTL formula. The intuitive meaning of the CTL operators can be seen in Figure 2.2 where for each formula a satisfying example computation tree is given.

**Bounded model checking.** Bounded model checking was introduced in [Bie+99] as a method based on SAT (Boolean satisfiability problem) solvers looking for counterexamples with iteratively increasing lengths. This idea can be generalised: bounded model checking evaluates the given temporal logic

Figure 2.2: Examples of CTL operators

formula by iteratively checking greater and greater part of the model until the satisfaction of the requirement can be decided (*see Def. A.7*, *p. 124*).

#### 2.2 Related Work

This section overviews the work related to this chapter. As the goal of this work is to improve the saturation-based techniques, the focus is set to the various saturation algorithms proposed in the past.

#### 2.2.1 Bounded Model Checking

Early symbolic model checking methods based on binary decision diagrams (BDDs) improved the scalability of model checking, making possible to use this verification method on industrial examples [Bur+92]. Although this pushed the limits of model checking compared to the explicit model checking algorithms, the memory bottleneck was still severe. Bounded model checking using SAT solver was proposed in [Bie+99] as a complementary technique. SAT-based model checking was widely considered more applicable than BDD-based methods [Bie+03; Aml+05]. Some authors have stated explicitly that BDD-based model checking is unable to "handle large state spaces of 'real world' designs" [Cha+02].

Bounded model checking is widely considered as a purely SAT-based method (e.g. [Aml+05]), however its principles can be implemented using other technologies too.

#### 2.2.2 Saturation-Based Techniques

Saturation was first introduced in [CLS01] as a symbolic state space exploration method. Typically, the set of reachable states (the state space) is not explicitly given (enumerated) by a formal model, it has to be determined based on the initial state(s) and the next-state function. The simplest solution for that is a breadth- or depth-first search (BFS or DFS). Their time complexity is  $O(|\mathcal{S}|)$ , where  $|\mathcal{S}|$  is the number of reachable states. In case of asynchronous systems, where many components are loosely coupled, this is not efficient. Imagine a system with two independent components, having n and m reachable states respectively. It is intuitive that the O(nm) complexity of BFS could be reduced to O(n+m) due to the independence.

This is the high-level motivation of saturation for checking state spaces of components in isolation as much as possible [CMS03]. Given a discrete-state model decomposed into K (not necessarily independent) parts (components), saturation determines the set of reachable states  $\mathcal{S}$ . Formally, the input model is as follows.

#### Definition 2.1 (Input model of saturation [CS03]).

A discrete-state model is a 4-tuple  $M = \langle \hat{\mathcal{S}}, \mathcal{S}_0, \mathcal{E}, \mathcal{N} \rangle$ , where:

- $\hat{S} = S_K \times \cdots \times S_1$  is the potential state space, decomposed into K parts ( $S_i$  is the local state space of component i);

- $S_0 \subseteq \hat{S}$  is the set of initial states;

- $\mathcal{E}$  is the set of events; and

- $\mathcal{N} \subseteq \hat{\mathcal{S}} \times \hat{\mathcal{S}}$  is the next-state relation. It can also be regarded as a function  $\mathcal{N} : \hat{\mathcal{S}} \to 2^{\hat{\mathcal{S}}}$ , where  $\mathcal{N}(\mathbf{s}) = \{\mathbf{s}' : (\mathbf{s}, \mathbf{s}') \in \mathcal{N}\}$ .

The local state spaces  $S_1, \ldots, S_K$  do not have to be explicitly given, as they can be explored onthe-fly [CMS03]. Furthermore, typically the  $\mathcal N$  next-state relation is not given explicitly either, but based on the given high-level model  $\mathcal N(\mathbf s)$  can be determined for a given  $\mathbf s$  (e.g. a Petri net implicitly defines  $\mathcal N$ ). Notice that as the global state space is decomposed, each global state  $\mathbf s \in \mathcal S$  is a composition of local states:  $\mathbf s = (s_K, s_{K-1}, \ldots, s_1)$ , where each  $s_i \in \mathcal S_i$ .

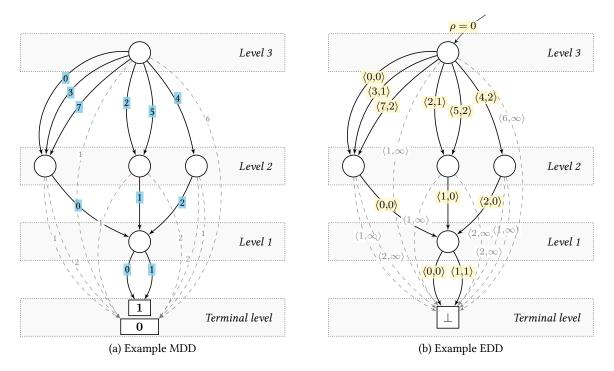

EXAMPLE. An example MDD can be seen in Figure 2.3(a) that encodes the following set (in  $x_3, x_2, x_1$  order):

```

\mathcal{S} = \{ (0,0,0), (3,0,0), (7,0,0), (2,1,0), (5,1,0), (4,2,0), (0,0,1), (3,0,1), (7,0,1), (2,1,1), (5,1,1), (4,2,1) \}.

```

Let us assume the following local state space encodings for the example Petri net in Figure 2.1.

```

\begin{array}{llll} \textit{Component 3:} & \left\{ & 0 \mapsto \langle M(p_4) = 2, M(p_5) = 0 \rangle, & 1 \mapsto \langle M(p_4) = 3, M(p_5) = 0 \rangle, \\ & 2 \mapsto \langle M(p_4) = 1, M(p_5) = 0 \rangle, & 3 \mapsto \langle M(p_4) = 1, M(p_5) = 1 \rangle, \\ & 4 \mapsto \langle M(p_4) = 0, M(p_5) = 0 \rangle, & 5 \mapsto \langle M(p_4) = 0, M(p_5) = 1 \rangle, \\ & 6 \mapsto \langle M(p_4) = 2, M(p_5) = 1 \rangle, & 7 \mapsto \langle M(p_4) = 0, M(p_5) = 2 \rangle & \right\} \\ \textit{Component 2:} & \left\{ & 0 \mapsto \langle M(p_3) = 0 \rangle, & 1 \mapsto \langle M(p_3) = 1 \rangle, \\ & 2 \mapsto \langle M(p_3) = 2 \rangle & \right\} \\ \textit{Component 1:} & \left\{ & 0 \mapsto \langle M(p_1) = 1, M(p_2) = 0 \rangle, & 1 \mapsto \langle M(p_1) = 0, M(p_2) = 2 \rangle & \right\} \\ \end{array}

```

Given these symbolic state encodings, the MDD in Figure 2.3(a) encodes the reachable state set of the Petri net in Figure 2.1.

The local state encodings in the above example were generated by the saturation algorithm. One can see that some local states are impossible to reach, e.g. state 1 of component 3. This is a side-effect of the on-the-fly local state space exploration. When a new potential local state is found, it is called *unconfirmed*. A local state that is later found to be globally reachable (i.e. it is part of a reachable global state) is called *confirmed*.

CTL model checking with saturation. As mentioned above, saturation was first introduced as a state space exploration algorithm. The state space exploration is practically the computation of the fixed point  $S_0 \cup \mathcal{N}(S_0) \cup \mathcal{N}^2(S_0) \cup \cdots = \mathcal{N}^*(S_0)$  (where \* denotes the reflexive and transitive closure [CMS06]). Based on this, saturation was later generalised as a fixed point computation algorithm and used for instance for CTL model checking, introduced first in [CS03]. CTL typically defines eight temporal operators (EX, EF, EG, EU, AX, AF, AG, AU), but it is enough to implement a (not necessarily minimal) generator subset of them. For example, each A operator can be expressed using E operators, therefore [CS03] proposes implementations only for the E operators.

The implementation of EX and EF operators is simple. EX can be formalised as follows:  $\mathbf{s} \models \mathsf{EX}\ p$  iff  $\exists \mathbf{s}' \in \mathcal{N}(\mathbf{s}) \colon \mathbf{s}' \models p$ . Therefore if the set P of reachable states satisfying p ( $P \subseteq \mathcal{S}$ ) is known, checking  $\mathbf{s} \models \mathsf{EX}\ p$  is equivalent to checking  $\mathbf{s} \stackrel{?}{\in} \mathcal{N}^{-1}(P)$ . With similar reasoning, checking  $\mathbf{s} \models \mathsf{EF}\ p$  (i.e. whether a state satisfying p is reachable from  $\mathbf{s}$ ) can be reduced to checking  $\mathbf{s} \stackrel{?}{\in} (\mathcal{N}^{-1})^*(P)$ , which is a similar problem to determining the reachable state space of the model (i.e.  $\mathcal{N}^*(\mathcal{S}_0)$ ). The implementation of EG and EU operators are less straightforward in symbolic settings and for the details we refer the reader to  $[\mathsf{CS03}]^1$ .

Constrained saturation. Constrained saturation was proposed by Zhao *et al.* in [ZC09] as an improvement for the CTL model checking. It limits the exploration to a given state set. While this can easily be achieved using the intersection MDD operation, MDD operations are typically expensive. Instead of the "step-and-cut" strategy (with intersections after each step), they have proposed a "check-and-step" strategy, where the constraint state set, encoded also by MDD, is simultaneously traversed and used for constraining the exploration. The implementation of EU operator with constrained saturation proved to be more efficient than the traditional approach. The formal details of constrained saturation can be found in [ZC09].

**Bounded state space exploration with saturation.** Saturation can efficiently store the reachable state space, but this does not mean that it can cope with every problem with reasonable amount of resources. Bounded model checking techniques are powerful when the requirement can be evaluated based on a fraction of the complete state space, for example to find shallow error states. However, the "non-standard search strategy" that makes saturation powerful in state space exploration makes its application for bounded state space exploration difficult [YCL09].

To perform saturation-based bounded exploration, the state distances (i.e. the minimum number of transitions to be fired to reach the state, see Def. A.3) have to be stored. Yu *et al.* [YCL09] considered different variants of decision diagrams. In the following, we will use their approach building on edge-valued MDDs (EV<sup>+</sup>MDDs or EDDs) (see Def. A.9, p. 125), which were also used in [CS02]. EDDs encode functions  $D_K \times \cdots \times D_1 \to \mathbb{N} \cup \{\infty\}$ . They can be regarded as extended MDDs, where each edge is additionally labelled with a non-negative integer (or  $\infty$ ). Contrarily to MDDs, it is sufficient to have one leaf node in EDDs, the node  $\bot$ . A path from the root node to the leaf node  $\bot$  maps the sum of the edge labels to the tuple encoded by the path.

Example. An example EDD can be seen in Figure 2.3(b) that encodes the following mappings:

<sup>&</sup>lt;sup>1</sup>A saturation-based method was given for EG in [CS03], but even the authors of the paper consider its performance typically worse than the traditional greatest fixed point algorithm. The saturation-based implementation of EU was much better, but it was later significantly improved further in [ZC09].

Figure 2.3: Example decision diagrams (describing the symbolic state space of the Petri net shown in Figure 2.1)

$$\{ \quad (0,0,0) \mapsto 0, (3,0,0) \mapsto 1, (7,0,0) \mapsto 2, (2,1,0) \mapsto 1, (5,1,0) \mapsto 2, (4,2,0) \mapsto 2, \\ (0,0,1) \mapsto 1, (3,0,1) \mapsto 2, (7,0,1) \mapsto 3, (2,1,1) \mapsto 2, (5,1,1) \mapsto 3, (4,2,1) \mapsto 3 \quad \}$$

Given the state encodings discussed in the previous example, the EDD in Figure 2.3(b) encodes the reachable state set of the Petri net in Figure 2.1 with distance information (i.e. the EDD maps to each symbolic state its distance from the initial state (0,0,0)).

The calculated and stored distance information is then used to limit the state space exploration to the states with distance values less than or equal to the given bound. In case of BFS, it is easy to terminate the exploration when the bound is reached. However, the advantage of saturation makes this more challenging too. To overcome this challenge, Yu  $et\,al.$  added an explicit pruning after each step. Two pruning strategies were proposed: an exact method that strictly computes the bounded state space with respect to the given bound b, and an approximative method that is faster, but provides weaker guarantees: it only ensures that each state within bound b will be included and each state with distance more than  $K \cdot b$  will be excluded from the state space (where K is the number of components in the model).

As the saturation-based techniques will be used for B-I-Sat as building blocks, deeper details are not necessary at this point. For more details we refer to [CLS01; CMS03; CZJ12]. The parts related to the contributions presented here are discussed in [a30], along with the pseudocode of the contributions. An overview and short summary of the main saturation-related papers is in Table 2.1.

Ref. Year Contents, new contributions [CLS00] 2000 First discussion of the main saturation concepts [CLS01] The first paper drawing up the idea of saturation, a novel, MDD-based state space exploration 2001 algorithm [CS02] 2002 State space exploration with state distances to generate shortest traces [CMS03] 2003 Extension of saturation with automated explicit *local state space* discovery [CS03] 2003 CTL model checking based on the saturation algorithm [CY05] 2005 Conjunctive and disjunctive partitioning [ZC09] 2009 Constrained saturation to improve the efficiency of CTL model checking [YCL09] Bounded reachability checking based on saturation 2009 2012 Extension of saturation to coloured Petri net models [c28][*j*26] 2014 Introduction of the *lazy coloured saturation* [CMS06] 2006 Summary and deep analysis of the previous saturation algorithms [CZJ12] 2012 Summary of the first ten years of saturation

Table 2.1: Milestones of the saturation algorithm

#### 2.2.3 Bounded Model Checking With Decision Diagrams

Combining different model checking approaches is not unheard-of in the field of formal verification. For example, Chauhan *et al.* [Cha+02] combine SAT-based and BDD-based methods, where BDD-based model checking is only used on abstract models. The first work truly combining bounded model checking and decision diagram-based methods was done by Copty *et al.* [Cop+01] in 2001. Later, Cabodi *et al.* [CNQ05] used BDD-based bounded model checking and they have found that their approach can "deal with larger problems than other BDD-based tools" and that their "methodology seems to be more scalable with deeper bugs" than SAT-based bounded model checking methods [CNQ05].

The author is not aware of any work on combining bounded model checking principles with saturation-based techniques before the own work [c18].

#### 2.3 Overview of the B-I-Sat Algorithm

This section presents the collected building blocks which can be used for a bounded saturation-based model checking algorithm. Then the high-level workflow of *B-I-Sat* (Bounded Iterative Saturation) is discussed. B-I-Sat is a novel CTL model checking algorithm that combines bounded model checking and saturation-based techniques. Finally, the arisen challenges and design questions are discussed.

#### 2.3.1 Building Blocks

Here we review the main saturation-based techniques to collect the already existing building blocks that can be reused for the B-I-Sat algorithm.

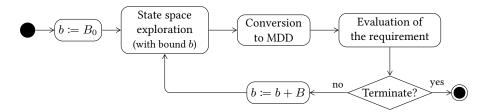

**Unbounded saturation-based model checking.** The classic saturation-based CTL model checking [CS03] is a two-step procedure: first it explores the reachable state space, then the given CTL formula is evaluated, as can be seen in Figure 2.4.

It is easy to identify the following two building blocks.

State space exploration: It collects all reachable states in a given model from a given initial state.

- Input: Petri net (with initial marking and decomposition defined);

- *Outputs:* reachable state space S (MDD); next-state function N (MDD);

- *Internal results*: local state spaces  $S_k$ ; caches for the saturation functions and the decision diagram operations.

CTL formula evaluation: It evaluates the satisfaction of a given CTL formula on the given explored model.

- Inputs: state space S (MDD); initial state(s)  $S_0$  (MDD); next-state function N (MDD); CTL formula f;

- Output: Boolean result (true iff f is satisfied on S by  $S_0$ ) and optionally the subset of S which satisfies f;

- Internal results: caches for the saturation functions and the decision diagram operations.

**Bounded state space exploration.** The bounded state space exploration [ZC09] is a single-step process, it will be considered as a single building block. Let us introduce a new notation:  $S_{[a;b]} \triangleq \{s \in S : a \leq \delta(s) \leq b\}$ , i.e.  $S_{[a;b]}$  is the partial state space containing all states with distances between a and b (both inclusive).

Bounded state space exploration (with exact truncation strategy): It collects all reachable states from a given initial state in a given model which are within a given distance b.

- *Input:* Petri net (with initial marking and decomposition defined); bound *b*;

- Output: reachable (partial or bounded) state space  $S_{[0;b]}$  (EDD); (partial) next-state function  $\mathcal{N}$  (MDD);

- Internal result: local state spaces  $S_k$ ; caches for the saturation functions and the decision diagram operations.

Note that only the exact truncation (pruning) strategy ensures that the resulting state space is  $S_{[0;b]}$ . The approximative truncation ensures only that the resulting state space S' contains all states within bound b and contains no states with distance more than  $K \cdot b$ :  $S_{[0;b]} \subseteq S' \subseteq S_{[0;K \cdot b]}$ .

#### 2.3.2 Sketching Up the B-I-Sat Algorithm

To achieve the goal and to design a bounded saturation-based CTL model checking algorithm, two key challenges should be met. First, the unbounded saturation-based algorithm should work on a partial (bounded) state space, using the bounded state space exploration algorithm. Second, the algorithm should be made iterative, to check the CTL formula on an increasingly large part of the full state space.

Figure 2.4: Overview of the classic saturation-based model checking

Non-iterative bounded model checking with saturation. The apparent challenge of integrating the bounded state space exploration to the saturation-based CTL model checking based on the discussion in Section 2.3.1 is the mismatch between the state space encodings: the explored partial state space is encoded by an EDD, while the CTL evaluation works on an MDD state space. The CTL evaluation could be modified to handle EDDs, but this might have a negative impact on the performance, as the MDD representation of the state space is typically more compact than the EDD representation. The basic CTL evaluation algorithm cannot benefit from the distance information, therefore they can be dropped from the EDD. An MDD which encodes a state set contains a state s if the corresponding path leads to the node 1. In an EDD which encodes a state set, a state s is contained if the corresponding path leading to the terminal node has a finite weight. Therefore if the EDD encodes a function  $f_E$ , the corresponding MDD should encode the function  $f_M$  as follows [a31]:

$$f_M(x_n,\ldots,x_1) = \begin{cases} 0, & \text{if } f_E(x_n,\ldots,x_1) = \infty \\ 1, & \text{if } f_E(x_n,\ldots,x_1) < \infty \end{cases}$$

This can be used to construct an MDD corresponding to the state set encoded by the EDD for the CTL formula evaluation. This transformation has a linear time complexity in the number of EDD nodes. The MDD representing the set encoded by the EDD  $\mathcal E$  without the distance information will be denoted by  $MDD(\mathcal E)$ . Similarly, let us denote by  $EDD(\mathcal M)$  the EDD which maps the value 0 exactly to the tuples contained by the MDD  $\mathcal M$ , and maps  $\infty$  to all the other tuples.

The second problem is less apparent and it is related to the pruning during bounded state space exploration. The pruning step will remove the states that are not within the given bound, but this does not modify the next-state relation. Therefore the CTL formula evaluation may consider states that are not included in the bounded state space. This is not a threat to correctness, but it reduces the advantage of bounded model checking [e21; c17]. This challenge will be discussed later in detail.

If these challenges are solved, a simple, non-iterative, saturation-based bounded model checking algorithm can be drawn up, as shown in Figure 2.5. Obviously, this is not useful in practice yet, as in cases where the bound is not chosen correctly, the result will not be representative of the whole state space. Knowing the smallest necessary bound value a priori is typically not possible.

Figure 2.5: Overview of the non-iterative, saturation-based bounded model checking

**Iterative bounded model checking with saturation.** The need to know the correct bound value can be eliminated by making the model checking method presented in Figure 2.5 iterative. Looking at a high level this is simple: the state space should be explored up to an increasing bound b, until a representative result is available and the procedure can be terminated. This is the main idea of the B-I-Sat algorithm, depicted in Figure 2.6. However, if we take a closer look at different parts of the algorithm, various challenges and questions arise. They are discussed in the next section.

#### 2.3.3 Challenges and Solutions

Previously the high-level ideas of B-I-Sat were presented without details. In the following part of this section the main design questions, challenges and the given solutions are summarised.

Figure 2.6: Overview of the iterative, saturation-based bounded model checking (B-I-Sat)

- Initial bound and bound increment. Most SAT-based bounded model checking algorithms start with bound 0 and increment it by one in every iteration. This ensures to find the shortest counterexample and to explore the smallest necessary part of the state space. In case of saturation this might not be the most efficient strategy. Therefore the initial bound  $B_0$  and the bound increment B will not be fixed and can be used to parametrise the algorithm, depending on the current model and requirement. To simplify the discussion, in the following we will assume that  $B_0 = B$ , thus the bound b in iteration i is  $b = i \cdot B$ . However, all the presented strategies can be generalised to use initial bounds different from the increments ( $B_0 \neq B$ ).

- **Pruning strategy.** Contrarily to BFS, due to the irregular search order, an explicit pruning operation has to be included in the saturation algorithm. Two pruning strategies were proposed in [YCL09]: an exact truncation and a faster but approximative truncation. The approximative truncation had a better performance in [YCL09], however it was shown in [*c*18] that the use of caches can make the exact truncation strategy competitive. The choice of pruning strategy will not be fixed. In the following, we will generally assume the use of the exact truncation strategy, as it simplifies the notations and the discussion in the following.

- **Termination.** After the first exploration and evaluation steps, a result is available. However, this result does not necessarily hold for the whole state space. If it does, the model checking algorithm can terminate. Otherwise, a next iteration with greater bound is required. Deciding when to terminate the algorithm is not simple. This question will be addressed in detail in Section 2.5, and termination conditions will be proposed based on three-valued logic.

- Avoiding unreachable states during requirement evaluation. As it was discussed before, the next-state relation  $\mathcal{N}$  may contain transitions leaving states that are not included in the bounded state space. This implies that the CTL formula evaluation, which uses  $\mathcal{N}^{-1}$ , may include unreachable states in the resulting state sets. This is not a threat to correctness, but depending on the model it may significantly decrease the performance of the algorithm. A straightforward solution is to intersect the result in each iteration with the explored partial state space  $\mathcal{S}_{[0,b]}$ , but this might be an expensive operation. Similar problems were addressed in case of the evaluation of EU CTL operators in [ZC09]. The proposed solution, the constrained saturation restricts the exploration to a given set  $\mathcal{C}$ , without explicit intersection operation, resulting in a better performance. The same solution can be used for bounded CTL model checking as well: using constrained saturation, the exploration can be restricted to the explored partial state space  $\mathcal{S}_{[0,b]}$ . All proposed strategies will use constrained saturation for the CTL requirement evaluation part with the constraint  $\mathcal{C} = \mathcal{S}_{[0,b]}$ .

- **Reusing the produced data.** The state space exploration step results in various data: partial state space, next-state function, local state spaces, cache values, etc. Dropping all this data at the

beginning of each iteration and restarting the exploration without any knowledge about the previous iterations trivially results in a correct algorithm. However, keeping some of the data may improve the performance. In the following, various strategies will be discussed which mainly differ in this aspect, i.e. how do they reuse data from previous iterations. See Sections 2.3.4 and 2.4 for more details.

#### 2.3.4 Iteration Strategies

In this section two simple iteration strategies are proposed for B-I-Sat: the *restarting* and *continuing* strategies. The pseudocode of the presented iteration strategies can be found in Appendix B (p. 127).

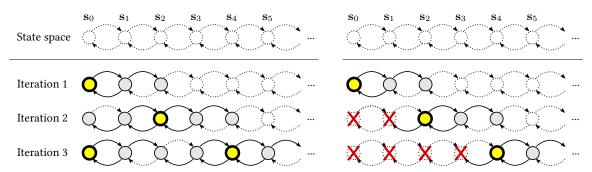

**Restarting strategy.** The simplest iteration strategy would be to start each iteration with no prior information. This strategy would start every iteration from the initial state (set)  $S_0$ , then explore the part  $S_{[0;i\cdot B]}$  in each iteration  $i=1,2,\ldots$  (where B is the given bound increment).

Based on Section 2.3.1, there are four types of data produced by the state space exploration: reachable state spaces (encoded by EDDs), local state sets, next-state relations, and cache data.

- The state space EDD built in the last iteration will be dropped. This is the simplest way to deal with the fact that increasing the bound will make some of the nodes unsaturated, i.e. some nodes will not represent fixed points anymore with respect to the next-state relation (which grows if the bound increases).

- The next-state relation  $(\mathcal{N})$  can grow only if a greater bound is used, therefore it can be reused and extended.

- The local state spaces ( $S_i$ ) can grow only if a greater bound is used, therefore the local state spaces from the previous iterations can be used as "hints" for the on-the-fly exploration algorithm and can improve the performance of saturation in iterations i > 1.

- The caches related to the state space EDD should be flushed, as their content is not valid after restarting the exploration. All other cache entries may be kept.

Figure 2.7 illustrates the restarting strategy. The yellow part (with a thick border) represents the initial state set used in each iteration. The grey parts symbolise the newly explored state sets. Algorithm B.1 (p. 128) shows the pseudocode of the restarting strategy. More details about the implementation can be found in [a30].

|             | State space $(S')$ | Part encoded by $\mathcal{S}'$ |

|-------------|--------------------|--------------------------------|

| Iteration 1 | $ \leftarrow $     | [0; B]                         |

| Iteration 2 |                    | $[0;2\cdot B]$                 |

| Iteration 3 |                    | $[0;3\cdot B]$                 |

Figure 2.7: Illustration of the restarting strategy (based on [*a*30])

Here we assume that the exact truncation is used as pruning strategy. However, the restarting strategy can be used with the approximative truncation as well. In this case, obviously the partial state space explored in iteration i will be a superset of  $S_{[0:i\cdot B]}$ .

**Continuing strategy.** At first look it seems to be wasteful to restart each iteration from the initial state of the model, as for every bound b' > b:  $S_{[0;b]} \subseteq S_{[0;b']}$ , i.e. every state s found in iteration i will be found in every future iteration, with the same distance value. This motivated the continuing strategy, which starts every iteration i > 1 from the result state space of iteration i - 1 as initial state set. The details of the minor technical modifications required on the saturation-based state space to support this are discussed in [a30].

It is important to notice that it is not known at the beginning of an iteration, which nodes are saturated (i.e. no new states can be found from them) and which are not, thus it is required to resaturate (i.e. to recompute the fixed points) every node. This may be an expensive operation, but it is not obvious whether this needs more or less resources compared to the restarting strategy. This question will be addressed in the evaluation section (see Section 2.6). In every other detail the continuing strategy works in the same way as the restarting strategy.

Figure 2.8 illustrates the continuing strategy. The yellow part (with a thick border) represents the initial state set used in each iteration. The grey parts symbolise the newly explored state sets. Algorithm B.2 (p. 128) shows the pseudocode of the continuing strategy. More details about the implementation can be found in [a30].

|             | State space $(S')$ | Part encoded by $\mathcal{S}'$ |

|-------------|--------------------|--------------------------------|

| Iteration 1 |                    | [0;B]                          |

| Iteration 2 |                    | $[0;2\cdot B]$                 |

| Iteration 3 |                    | $[0;3\cdot B]$                 |

Figure 2.8: Illustration of the continuing strategy based on [a30])

Here we have assumed that the exact truncation was used as a pruning strategy, but just as in the case of the restarting strategy, the approximate truncation can be used as well.

The next section introduces a third, more complex strategy, the compacting strategy.

**Publications related to this section.** The first analysis of combining bounded state space exploration and saturation-based CTL model checking was presented in [c18; a32], then more details were discussed in [a31; a30]. The presented discussion of the challenges and the given solutions are based on [a30]. The idea to improve the algorithm by using constrained saturation was described in [e21] and the details of the improved version were presented in [e17]. The restarting strategy was first presented in [e18], the continuing strategy in [e17].

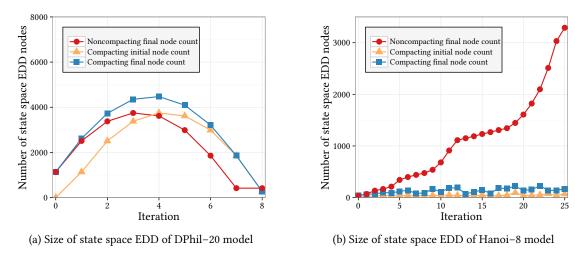

#### 2.4 Compacting Saturation Strategy<sup>2</sup>

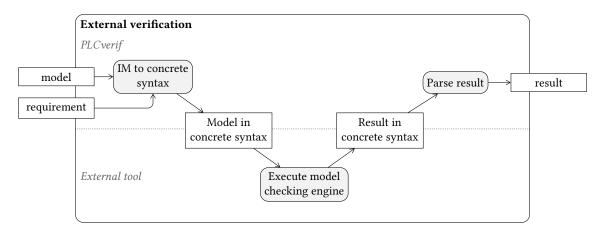

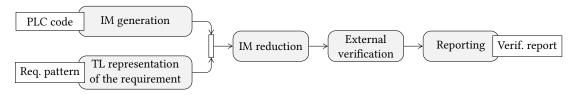

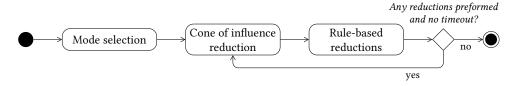

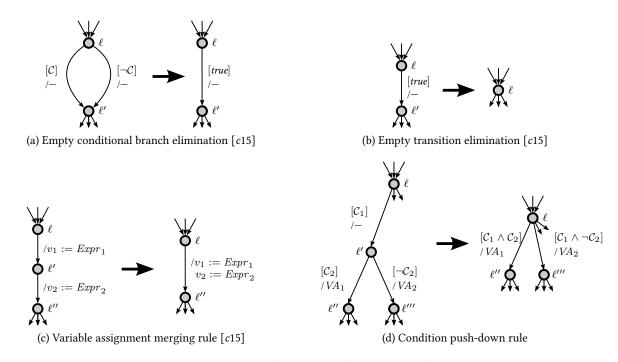

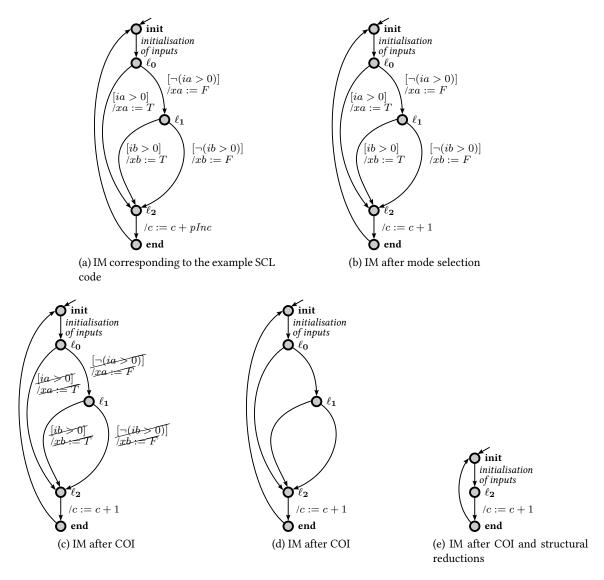

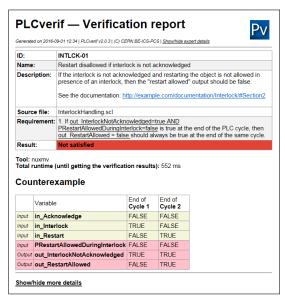

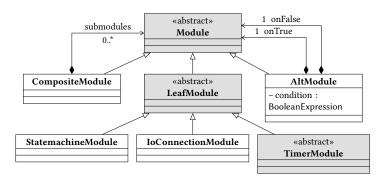

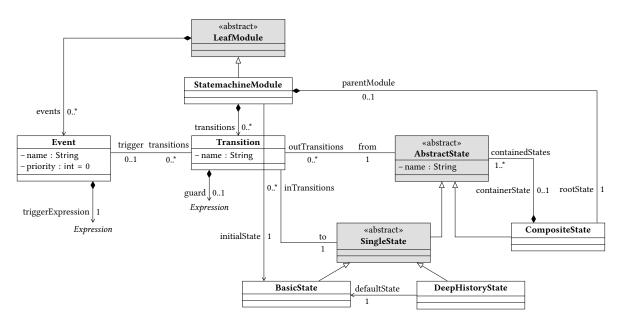

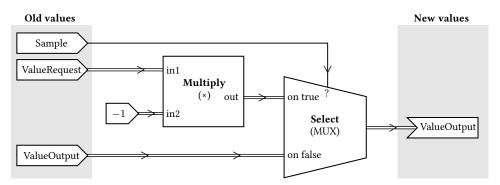

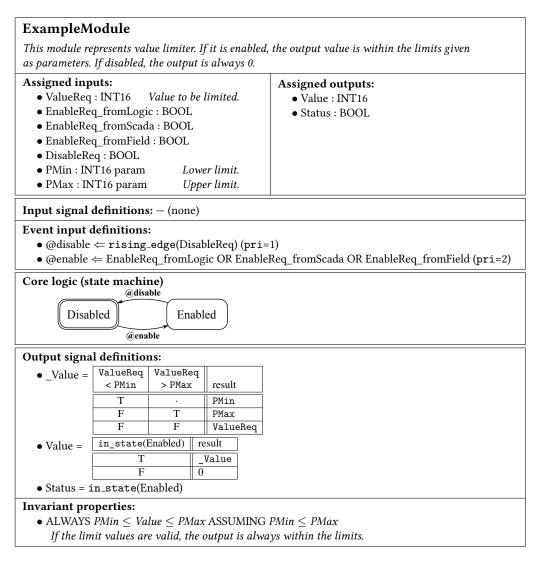

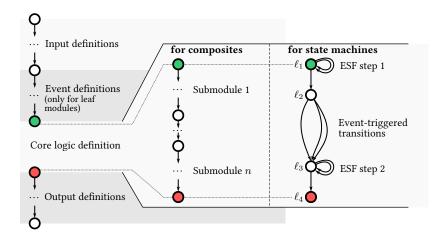

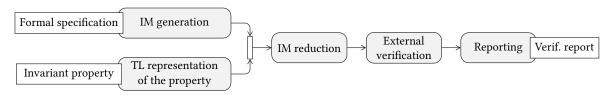

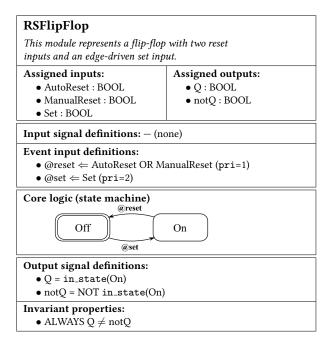

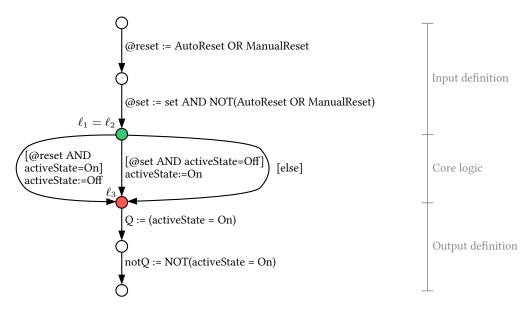

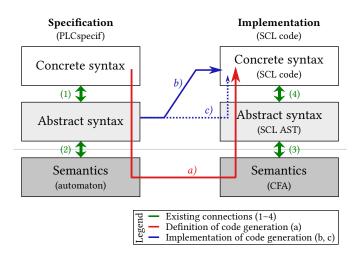

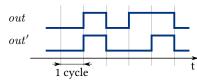

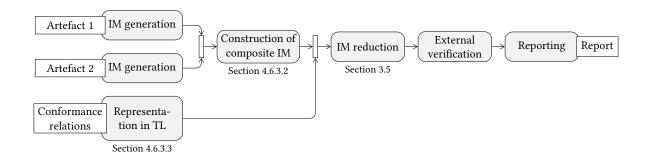

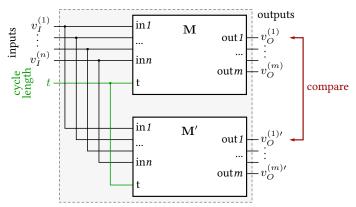

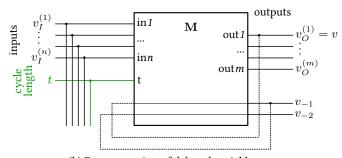

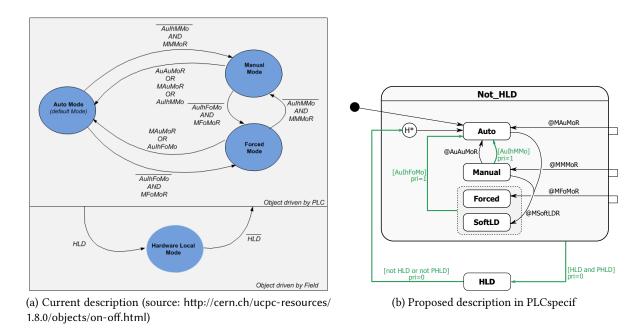

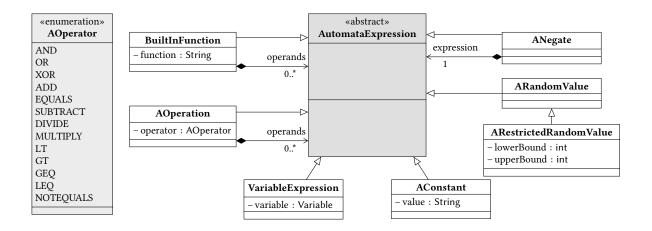

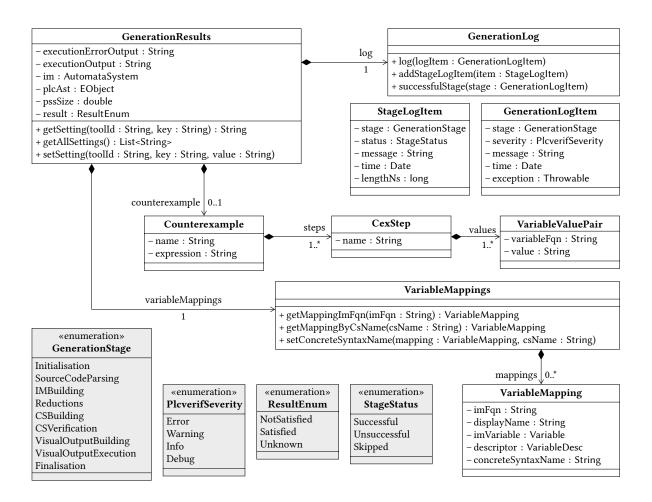

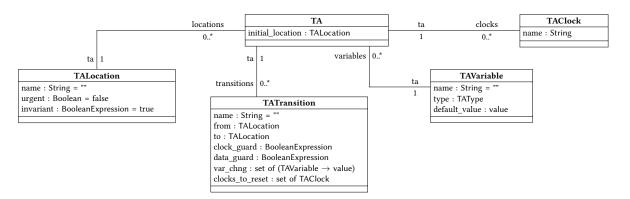

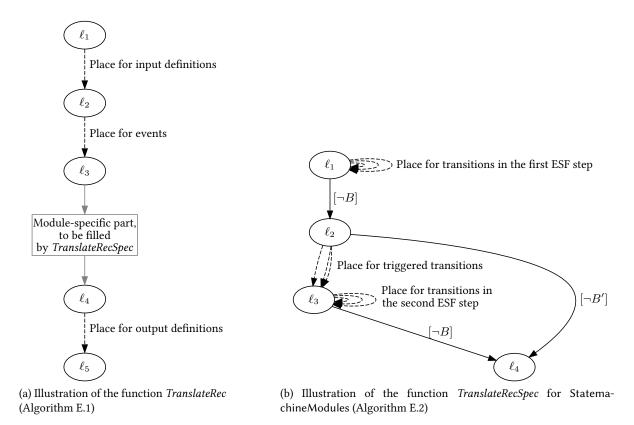

Both the restarting and the continuing strategies have a potential weakness: they store the whole [0;b] part of the state space (i.e.  $S_{[0;b]}$ , the states with distances between 0 and b) in a single EDD. The algorithms use EDDs for storing the distance information from the initial state along with each state, which is not possible in case of the simple MDD encoding. This information is necessary to limit the state space exploration at the bound b. The storage of the distance has its price to pay: the EDD representation of the state space is typically less compact than the MDD representation (without the distance information) would be.